Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

簡體網頁||繁體網頁

Hardware Design and Petri Nets pdf epub mobi 著者簡介

Hardware Design and Petri Nets pdf epub mobi 圖書描述

Hardware Design and Petri Nets presents a summary of the state of the art in the applications of Petri nets to designing digital systems and circuits. The area of hardware design has traditionally been a fertile field for research in concurrency and Petri nets. Many new ideas about modelling and analysis of concurrent systems, and Petri nets in particular, originated in theory of asynchronous digital circuits. Similarly, the theory and practice of digital circuit design have always recognized Petri nets as a powerful and easy-to-understand modelling tool. The ever-growing demand in the electronic industry for design automation to build various types of computer-based systems creates many opportunities for Petri nets to establish their role of a formal backbone in future tools for constructing systems that are increasingly becoming distributed, concurrent and asynchronous. Petri nets have already proved very effective in supporting algorithms for solving key problems in synthesis of hardware control circuits. However, since the front end to any realistic design flow in the future is likely to rely on more pragmatic Hardware Description Languages (HDLs), such as VHDL and Verilog, it is crucial that Petri nets are well interfaced to such languages. Hardware Design and Petri Nets is divided into five parts, which cover aspects of behavioral modelling, analysis and verification, synthesis from Petri nets and STGs, design environments based on high-level Petri nets and HDLs, and finally performance analysis using Petri nets. Hardware Design and Petri Nets serves as an excellent reference source and may be used as a text for advanced courses on the subject.

Hardware Design and Petri Nets pdf epub mobi 圖書目錄

下載連結1

下載連結2

下載連結3

發表於2025-03-06

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

喜欢 Hardware Design and Petri Nets 電子書 的读者还喜欢

Hardware Design and Petri Nets pdf epub mobi 讀後感

圖書標籤:

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

Hardware Design and Petri Nets pdf epub mobi 用戶評價

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

分享鏈接

Hardware Design and Petri Nets 2025 pdf epub mobi 電子書 下載

相關圖書

-

水産動物育種學 2025 pdf epub mobi 電子書 下載

水産動物育種學 2025 pdf epub mobi 電子書 下載 -

生物餌料培養學 2025 pdf epub mobi 電子書 下載

生物餌料培養學 2025 pdf epub mobi 電子書 下載 -

Proceedings of the 1990 Acm Sigmod International Conference on Management of Data, May 23-25, 1990, 2025 pdf epub mobi 電子書 下載

Proceedings of the 1990 Acm Sigmod International Conference on Management of Data, May 23-25, 1990, 2025 pdf epub mobi 電子書 下載 -

三網養魚技術 2025 pdf epub mobi 電子書 下載

三網養魚技術 2025 pdf epub mobi 電子書 下載 -

水産動物疾病學 2025 pdf epub mobi 電子書 下載

水産動物疾病學 2025 pdf epub mobi 電子書 下載 -

Sundae Girl 2025 pdf epub mobi 電子書 下載

Sundae Girl 2025 pdf epub mobi 電子書 下載 -

Scarlett 2025 pdf epub mobi 電子書 下載

Scarlett 2025 pdf epub mobi 電子書 下載 -

Lucky Star 2025 pdf epub mobi 電子書 下載

Lucky Star 2025 pdf epub mobi 電子書 下載 -

林蛙養殖 2025 pdf epub mobi 電子書 下載

林蛙養殖 2025 pdf epub mobi 電子書 下載 -

我國南方怎樣種好鮮食棗 2025 pdf epub mobi 電子書 下載

我國南方怎樣種好鮮食棗 2025 pdf epub mobi 電子書 下載 -

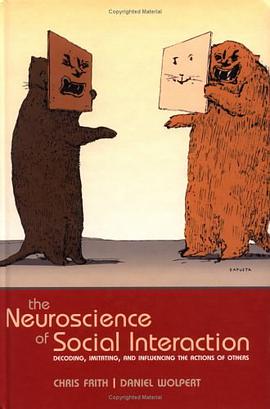

The Neuroscience of Social Interaction 2025 pdf epub mobi 電子書 下載

The Neuroscience of Social Interaction 2025 pdf epub mobi 電子書 下載 -

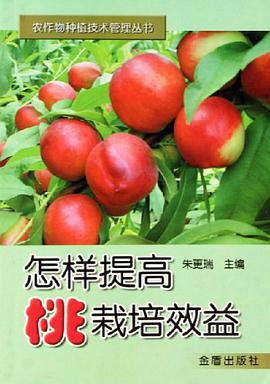

怎樣提高桃栽培效益 2025 pdf epub mobi 電子書 下載

怎樣提高桃栽培效益 2025 pdf epub mobi 電子書 下載 -

蔬菜良種與栽培指南 2025 pdf epub mobi 電子書 下載

蔬菜良種與栽培指南 2025 pdf epub mobi 電子書 下載 -

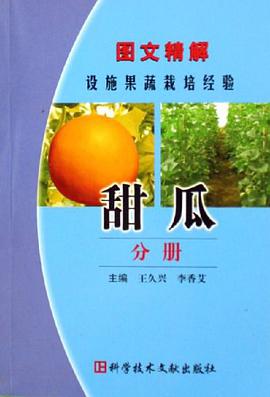

黃瓜分冊 2025 pdf epub mobi 電子書 下載

黃瓜分冊 2025 pdf epub mobi 電子書 下載 -

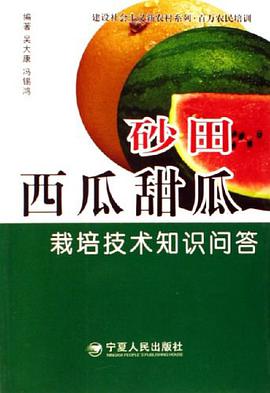

砂田西瓜甜瓜栽培技術知識問答 2025 pdf epub mobi 電子書 下載

砂田西瓜甜瓜栽培技術知識問答 2025 pdf epub mobi 電子書 下載 -

溫州花椰菜 2025 pdf epub mobi 電子書 下載

溫州花椰菜 2025 pdf epub mobi 電子書 下載 -

園藝植物保護概論 2025 pdf epub mobi 電子書 下載

園藝植物保護概論 2025 pdf epub mobi 電子書 下載 -

The Sapient Mind 2025 pdf epub mobi 電子書 下載

The Sapient Mind 2025 pdf epub mobi 電子書 下載 -

辣 2025 pdf epub mobi 電子書 下載

辣 2025 pdf epub mobi 電子書 下載 -

The Chimpanzees of the Budongo Forest 2025 pdf epub mobi 電子書 下載

The Chimpanzees of the Budongo Forest 2025 pdf epub mobi 電子書 下載